TMPZ84C015 を搭載したAKI-80ですが、メモリマップは前半がROM、後半がRAMの構成となっています。

今後、CP/Mを導入したいと思っていますので、どうしても前半のROMをRAMに切り替えして、64KフルRAMにする必要があります。

過去に制作してきたZ8S180ではレジスタを書き換えることでフルRAM化は簡単にできるのですが、AKI-80ではちょっと工夫が必要となります。そこで、AKIー80でのフルRAM化に挑戦してみました。

AKIー80本体の基板には変更を加えず、コネクタから出てきてる信号線と、ROMソケットからの信号線でROMとRAMを切り替えることとしました。

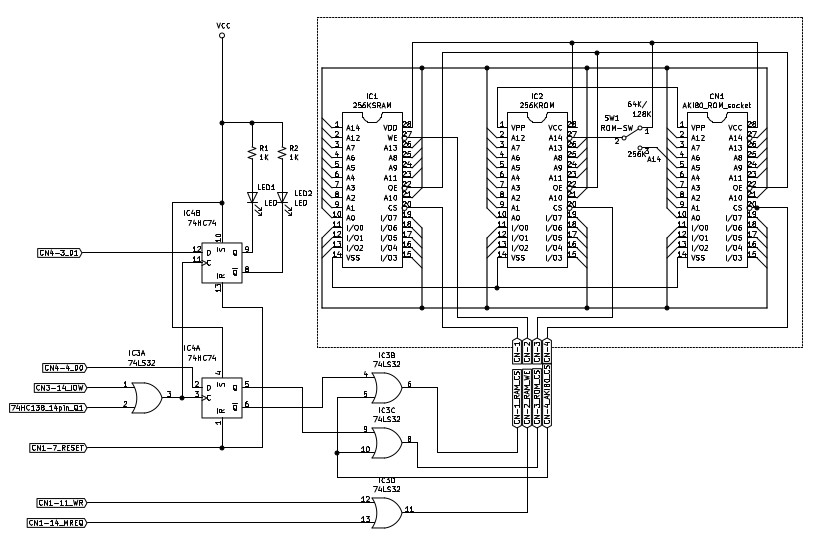

まずは、ROMソケットに接続されているCS(アドレスA15)が0x0000-0x7fffがROMに0x8000-0xffffがAKI-80基板のRAMに与えられている信号になりますので、0x0000-0x7fffが選択されている時に、ROMからRAMに切り変えたらいいことになります。(AKIー80本体のメモリのジャンパーはRAM/ROMとも256Kを選択)

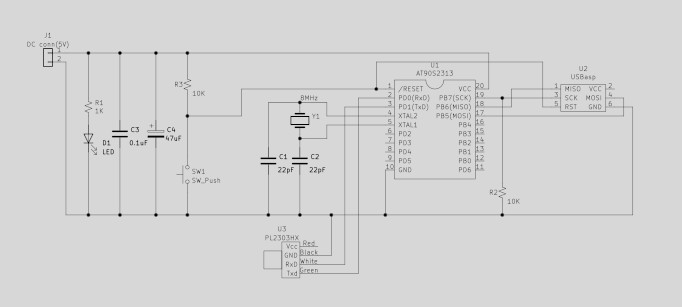

ROMからRAMの切り替えにはD-FF(74HC74)を使用して、このD-FFをアクセスしたとき(1を書き込んだ時)Qの反転信号と先ほどのCS信号とORをとることでRAMに切り替えます。

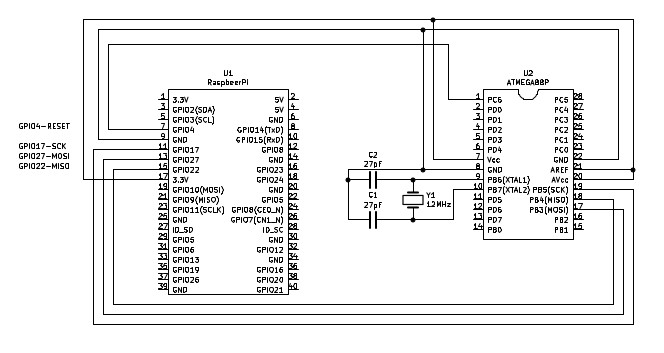

D-FFはI/Oマップに割り当て、以前制作した i2c回路の74HC138のQ1端子に接続します。D-FFのデータの切り替えは8bitデータのうちD0の書き込みで行います。

ROM/RAM 切り替えポート 0x84~0x87(A0-A1は未接続のため左記

アドレスが有効になります)

書き込みデータ 0x00 ROM選択(リセット時もROM)

0x03 RAM選択(D0-切り替え、D1-切り替えモニターLED)

また、ROMソケットには、RAMに必要な書き込み信号(WE)が来ていないので、74HC32(ORゲート)で新たに作成します。

実際の実装は、連結ソケット(両端オスピン28pin:秋月電子)を両面のユニバーサル基板に半田付けし、 連結ソケットの部品面にROM用のICソケットを(28pin)を亀の子状態で、半田付けしました。ただし、CS(20pin)は接続しないようにICソケット側のピンを曲げて信号をそれぞれ引き出しました。

連結ソケットの横に、RAM用のICソケットを半田付けし、並列接続します。

RAM用ICソケットの信号線はA14(1pin)の位置がROMの位置と違うので気を付けます。

また、RAMのWE(27pin)とCS(20pin)、ROMのCS(20pin)と連結ソケットのCS(20pin)の4つの信号はコネクターを経由してマザーボード側に接続しています。

追記:64K/128Kの容量のROMを使用する場合、PGM(27pin)がA14に接続されていると、Lowの場合PGMがアクティブになり、正常にアクセスできません。

64K/128KのROMの場合は、VCCに接続する必要があります。

下記の回路では、ROM-SWで64K/128Kと256KのROMを切り替えるように修正しました。

( AT28C64B で動作しないことでわかりました^^;2019/09/01回路図修正)

使用しているRAMはHM62256、ROMはAT28C64B(パラレルEEPROM)を使用しています。

実際の回路は、下記の通りです。