今回はRAMの動作確認を行っていきます。

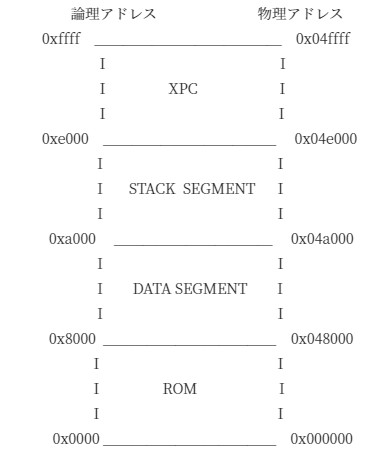

今回配置するRAMの論理アドレスと物理アドレスの関係は下記のようになります。

ROMは0x0000~0X7fffまでROM容量に応じてアドレスを占領します。

RAMは、64K論理アドレス空間の0x8000~0xffffを3分割します。

DATA SEGMENTとSTACK SEGMENTは任意の上位4ビットのアドレスを指定できますが、XPCの開始アドレス 0xe000は固定です。

DATA SEGMENTとSTACK SEGMENTの開始アドレスの指定は、SEGSIZEレジスタで指定します。上位4bitがSTACK SEGMENTの開始アドレス上位4ビットを指定し、下位4bitでDATA SEGNENTの開始アドレス上位4bitを指定します。

ここでは、

STACK SEGMENT = 0xa000 なので上位4bitは 0xa

DATA SEGMENT = 0x8000 なので上位4bitは 0x8

したがって、

SEGSIZE = 0xa8 になります。

論理アドレスを物理アドレスに関連付けるには、STACK SEGMENTの物理ベースアドレスSTAKSEGレジスタから論理アドレスを引いたアドレスとDATA SEGMENTの物理ベースアドレスDATASEGレジスタから論理アドレスを引いたアドレスを設定します。

各物理アドレスの上位8bitを指定します。

STACK SEGMENTの物理ベースアドレス 0x4a000-0xa000の上位8bitは 0x40

DATA SEGMENTの物理ベースアドレス 0x48000-0x8000の上位8bitは 0x40

したがって、

STACKSEG =0x40

DATASEG =0x40

XPCも同様に物理アドレスから論理アドレスを引いたアドレスの上位8bitを指定します。

XPCの物理ベースアドレス 0x4e000-0xe000の上位8bitは 0x40

したがって

xpc=0x40

XPCについては、ld xpc命令などでセグメント形式で可変することができるようで、この領域はいろいろ用途が広がっているみたいです。

以上のように、MMU関連のレジスタを設定することでRAMを論理アドレスに割り当てることができそうです。

実際にプログラムしていきます。

各レジスタを定義付けします。(MMIDRは定義付けだけ行っています)

;;MMU: Memory Bank 1 Control Ragister

MB1CR .equ 0x15

;;MMU: MMU Instruction/Data Register

MMIDR .equ 0x10

;;MMU: Data Segment Register(Z180 BBR)

DATASEG .equ 0x12

;;MMU: Segment Size Register(Z180 CBAR)

SEGSIZE .equ 0x13

;;MMU: Stack Segment Register(Z180 CBR)

STACKSEG .equ 0x11RAMを物理アドレスに関連付けます。

開始アドレス 0x04000(MB1CR) CS1、OE1、WE1で制御

ld a,0b00000101

ioi ld (MB1CR),a ;0x400000 Use /OE1 or /WE1 Use CS1 (RAM)

MMU関連の初期設定を行います。

STACKSEG =0x40

DATASEG =0x40

SEGSIZE = 0xa8

xpc=0x40

ld a,0x40 ;MMU Data Reg Physics address 0x40000 (CS1)

ioi ld (DATASEG),a

ld a,0x40 ;MMU Stack Reg Physics address 0x40000 (CS1)

ioi ld (STACKSEG),a

ld a,0xa8 ;MMU Segsize logic Data address 0x8000 (CS1:0x48000)

ioi ld (SEGSIZE),a ;MMU Segsize logic Stack address 0xa000 (CS1:0x4a000)

ld a,0x40 ;MMU XPC Physics address 0x40000 (CS1:0x4e000)

ld xpc,a

確認プログラムは、0x8000番地に0x80(CLK=Low)を書き込み、再度読み出し、CLK端子をLowにしてLEDを消灯します。

main:

ld a,0x80 ;CLK(1pin) low

ld hl,0x8000 ;ram top address 0x8000

ld (hl),a

ld a,(hl)

ioi ld (GOCR),a

loop:

jr loop 全体的なプログラムは下記のおとりです。

; rabbit2000 ram check

;

; rabbit2000 cpu

; rom 0000h -- 7fffh

; ram 8000h -- ffffh

; External clock 19.6608MHz

; assembler

; program start 0000H

; main 0100H

;

; assemblers ASxxxx and ASlink V5.10

; file name rabbit2000_ram_check.asm

; $ asrab -l -s -o rabbit2000_ram_check.asm

; $ aslink -i rabbit2000_ram_check

; $ rom-writer TL866-2 plus rabbit2000_ram_check.ihx

;

.r2k

.area TEST(ABS)

;;Global Control/Status Register

GCSR .equ 0x00

;;Global Output Control Register

GOCR .equ 0x0e

;;MMU: Memory Bank 0 Control Ragister

MB0CR .equ 0x14

;;MMU: Memory Bank 1 Control Ragister

MB1CR .equ 0x15

;;MMU: MMU Instruction/Data Register

MMIDR .equ 0x10

;;MMU: Data Segment Register(Z180 BBR)

DATASEG .equ 0x12

;;MMU: Segment Size Register(Z180 CBAR)

SEGSIZE .equ 0x13

;;MMU: Stack Segment Register(Z180 CBR)

STACKSEG .equ 0x11

.org 0x0000

jp start

.org 0x0080

start:

ld a,0b00001000 ;proc=OSC,pclk=osc,periodic interrupt=disable

ioi ld (GCSR),a

ld a,0x00

ioi ld (MB0CR),a ;0x000000 Use /OE0 Use CS0 (ROM)

ld a,0b00000101

ioi ld (MB1CR),a ;0x400000 Use /OE1 or /WE1 Use CS1 (RAM)

ld a,0x40 ;MMU Data Reg Physics address 0x40000 (CS1)

ioi ld (DATASEG),a

ld a,0x40 ;MMU Stack Reg Physics address 0x40000 (CS1)

ioi ld (STACKSEG),a

ld a,0xa8 ;MMU Segsize logic Data address 0x8000 (CS1:0x48000)

ioi ld (SEGSIZE),a ;MMU Segsize logic Stack address 0xa000 (CS1:0x4a000)

ld a,0x40 ;MMU XPC Physics address 0x40000 (CS1:0x4e000)

ld xpc,a

jp main

.org 0x0100

main:

ld a,0x80 ;CLK(1pin) low

ld hl,0x8000 ;ram top address 0x8000

ld (hl),a

ld a,(hl)

ioi ld (GOCR),a

loop:

jr loop

.end

HEXファイルです。

:03000000C38000BA

:200080003E08D33200003E00D33214003E05D33215003E40D33212003E40D33211003EA852

:0B00A000D33213003E40ED67C30001A7

:0D0100003E80210080777ED3320E0018FE75

:00000001FF

同じように、スタックを設定し、push、pop命令で確認しました。

main: ld sp,0xe000 ;stack pointer set

ld a,0x80 ;CLK(1pin) low

push af

nop

nop

pop af

ioi ld (GOCR),a

loop:

jr loop 全体のプログラムです。

; rabbit2000 ram check

;

; rabbit2000 cpu

; rom 0000h -- 7fffh

; ram 8000h -- ffffh

; External clock 19.6608MHz

; assembler

; program start 0000H

; main 0100H

;

; assemblers ASxxxx and ASlink V5.10

; file name rabbit2000_ram_sp_check.asm

; $ asrab -l -s -o rabbit2000_ram_sp_check.asm

; $ aslink -i rabbit2000_ram_sp_check

; $ rom-writer TL866-2 plus rabbit2000_ram_sp_check.ihx

;

.r2k

.area TEST(ABS)

;;Global Control/Status Register

GCSR .equ 0x00

;;Global Output Control Register

GOCR .equ 0x0e

;;MMU: Memory Bank 0 Control Ragister

MB0CR .equ 0x14

;;MMU: Memory Bank 1 Control Ragister

MB1CR .equ 0x15

;;MMU: MMU Instruction/Data Register

MMIDR .equ 0x10

;;MMU: Data Segment Register(Z180 BBR)

DATASEG .equ 0x12

;;MMU: Segment Size Register(Z180 CBAR)

SEGSIZE .equ 0x13

;;MMU: Stack Segment Register(Z180 CBR)

STACKSEG .equ 0x11

.org 0x0000

jp start

.org 0x0080

start:

ld a,0b00001000 ;proc=OSC,pclk=osc,periodic interrupt=disable

ioi ld (GCSR),a

ld a,0x00

ioi ld (MB0CR),a ;0x000000 Use /OE0 Use CS0 (ROM)

ld a,0b00000101

ioi ld (MB1CR),a ;0x400000 Use /OE1 or /WE1 Use CS1 (RAM)

ld a,0x40 ;MMU Data Reg Physics address 0x40000 (CS1)

ioi ld (DATASEG),a

ld a,0x40 ;MMU Stack Reg Physics address 0x40000 (CS1)

ioi ld (STACKSEG),a

ld a,0xa8 ;MMU Segsize logic Data address 0x8000 (CS1:0x48000)

ioi ld (SEGSIZE),a ;MMU Segsize logic Stack address 0xa000 (CS1:0x4a000)

ld a,0x40 ;MMU XPC Physics address 0x40000 (CS1:0x4e000)

ld xpc,a

jp main

.org 0x0100

main: ld sp,0xe000 ;stack pointer set

ld a,0x80 ;CLK(1pin) low

push af

nop

nop

pop af

ioi ld (GOCR),a

loop:

jr loop

.end

HEXファイルです。

:03000000C38000BA

:200080003E08D33200003E00D33214003E05D33215003E40D33212003E40D33211003EA852

:0B00A000D33213003E40ED67C30001A7

:0F0100003100E03E80F50000F1D3320E0018FE12

:00000001FF

次回はシリアル通信を確認していきたいと思います。